您正在看的SQLserver教程是:深入了解內存(一)。DRAM和SRAM基礎知識 RAM(Random Access Memory)隨機存取存儲器對於系統性能的影響是每個PC用戶都非常清楚的,所以很多朋友趁著現在的內存價格很低紛紛擴容了內存,希望借此來得到更高的性能。不過現在市場是多種內存類型並存的,SDRAM、DDR SDRAM、RDRAM等等,如果你使用的還是非常古老的系統,可能還需要EDO DRAM、FP DRAM(塊頁)等現在不是很常見的內存。對於很多用戶或者有一定經驗的高級用戶來說,他可能能說出Athlon XP和Pentium 4的主要不同點,能知道GeForce3和Radeon之間的區別,但是如果真的讓他說出各種內存之間的實現機理的主要差別或者解釋CAS 2和CAS 3之間的主要差別的話,就可能不是非常的清楚了。畢竟CPU和顯卡之類的東西更容易引起我們的興趣。我個人在這方面的知識也是比較片面甚至是一知半解的,所以一直在收集這個方面的資料。在網上有很多很好的資源,其中Ars technica、Aceshardware、simpletech等網站的資料對於我系統的了解這個方面的知識有很大的幫助。本文主要以Ars technica的文章為基礎編寫而成,為大家比較詳細的介紹RAM方面的知識。雖然RAM的類型非常的多,但是這些內存在實現的機理方面還是具有很多相同的地方,所以本文的將會分為幾個部分進行介紹,第一部分主要介紹SRAM和異步DRAM(asynchronous DRAM),在以後的章節中會對於實現機理更加復雜的FP、EDO和SDRAM進行介紹,當然還會包括RDRAM和SGRAM等等。對於其中同你的觀點相悖的地方,歡迎大家一起進行技術方面的探討。 存儲原理 為了便於不同層次的讀者都能基本的理解本文,所以我先來介紹一下很多用戶都知道的東西。RAM主要的作用就是存儲代碼和數據供CPU在需要的時候調用。但是這些數據並不是像用袋子盛米那麼簡單,更像是圖書館中用有格子的書架存放書籍一樣,不但要放進去還要能夠在需要的時候准確的調用出來,雖然都是書但是每本書是不同的。對於RAM等存儲器來說也是一樣的,雖然存儲的都是代表0和1的代碼,但是不同的組合就是不同的數據。讓我們重新回到書和書架上來,如果有一個書架上有10行和10列格子(每行和每列都有0-9的編號),有100本書要存放在裡面,那麼我們使用一個行的編號+一個列的編號就能確定某一本書的位置。如果已知這本書的編號87,那麼我們首先鎖定第8行,然後找到第7列就能准確的找到這本書了。在RAM存儲器中也是利用了相似的原理現在讓我們回到RAM存儲器上,對於RAM存儲器而言數據總線是用來傳入數據或者傳出數據的。因為存儲器中的存儲空間是如果前面提到的存放圖書的書架一樣通過一定的規則定義的,所以我們可以通過這個規則來把數據存放到存儲器上相應的位置,而進行這種定位的工作就要依靠地址總線來實現了。對於CPU來說,RAM就象是一條長長的有很多空格的細線,每個空格都有一個唯一的地址與之相對應。如果CPU想要從RAM中調用數據,它首先需要給地址總線發送地址數據定位要存取的數據,然後等待若干個時鐘周期之後,數據總線就會把數據傳輸給CPU。下面的示意圖可以幫助你很好的理解這個過程。上圖中的小園點代表RAM中的存儲空間,每一個都有一個唯一的地址線同它相連。當地址解碼器接收到地址總線送來的地址數據之後,它會根據這個數據定位CPU想要調用的數據所在的位置,然後數據總線就會把其中的數據傳送到CPU。上面所列舉的例子中CPU在一行數據中每次知識存取一個字節的數據,但是在現實世界中是不同的,通常CPU每次需要調用32bit或者是64bit的數據(這是根據不同計算機系統的數據總線的位寬所決定的)。如果數據總線是64bit的話,CPU就會在一個時間中存取8個字節的數據,因為每次還是存取1個字節的數據,64bit總線將不會顯示出來任何的優勢,women工作的效率將會降低很多。 從“線”到“矩陣” 如果RAM對於CPU來說僅僅是一條“線”的話,還不能體現實際的運行情況。因為如果實際情況真的是這樣的話,在實際制造芯片的時候,會有很多實際的困難,特別是在需要設計大容量的RAM的時候。所以,一種更好的能夠降低成本的方法是讓存儲信息的“空格”排列為很多行--每個“空格”對應一個bit存儲的位置。這樣,如果要存儲1024bits的數據,那麼你只要使用32x32的矩陣就能夠達到這個目的了。很明顯,一個32x32的矩陣比一個1024bit的行設備更緊湊,實現起來也更加容易。請看下圖:知道了RAM的基本結構是什麼樣子的,我們就下面談談當存儲字節的過程是怎樣的:上面的示意圖顯示的也僅僅是最簡單狀態下的情況,也就是當內存條上僅僅只有一個RAM芯片的情況。對於X86處理器,它通過地址總線發出一個具有22位二進制數字的地址編碼--其中11位是行地址,另外11位是列地址,這是通過RAM地址接口進行分離的。行地址解碼器(row decoder)將會首先確定行地址,然後列地址解碼器(column decoder)將會確定列地址,這樣就能確定唯一的存儲數據的位置,然後該數據就會通過RAM數據接口將數據傳到數據總線。另外,需要注意的是,RAM內部存儲信息的矩陣並不是一個正方形的,也就是行和列的數目不是相同的--行的數目比列的數目少。(後面我們在討論DRAM的過程中會講到為什麼會這樣) 上面的示意圖粗略的概括了一個基本的SRAM芯片是如何工作的。

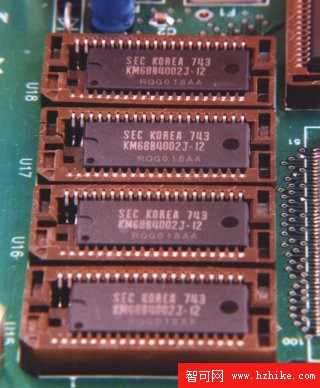

SRAM是“static RAM(靜態隨機存儲器)”的簡稱,之所以這樣命名是因為當數據被存入其中後不會消失(同DRAM動態隨機存儲器是不同,DRAM必須在一定的時間內不停的刷新才能保持其中存儲的數據)。一個SRAM單元通常由4-6只晶體管組成,當這個SRAM單元被賦予0或者1的狀態之後,它會保持這個狀態直到下次被賦予新的狀態或者斷電之後才會更改或者消失。SRAM的速度相對比較快,而且比較省電,但是存儲1bit的信息需要4-6只晶體管制造成本太高了(DRAM只要1只晶體管就可以實現)。 RAM芯片 前面的介紹都相對比較簡單、抽象。下面我們會結合實際的RAM芯片進行介紹。在談到這個問題的時候,我們會涉及到一個比較重要的技術:封裝。你應該聽說過諸如30線SIMMS、72線SIMMS和168線DIMMS或者RIMMs其中的一個或者幾個術語吧。如果要解釋這些術語之間的不同,就應該了解RAM的封裝技術。 SRAM芯片早期的SRAM芯片采用了20線雙列直插(DIP:Dual Inline Package)封裝技術,它們之所以具有這麼多的針腳,是因為它們必須:

首先你會看到地址引腳從14根變為7根,那麼這顆16K DRAM是如何完成同16K SRAM一樣的工作的呢?答案很簡單,DRAM通過DRAM接口把地址一分為二,然後利用兩個連續的時鐘周期傳輸地址數據。這樣就達到了使用一半的針腳實現同SGRAM同樣的功能的目的,這種技術被稱為多路技術(multiplexing)。那麼為什麼好減少地址引腳呢?這樣做有什麼好處呢?前面我們曾經介紹過,存儲1bit的數據SRAM需要4-6個晶體管但是DRAM僅僅需要1個晶體管,那麼這樣同樣容量的SRAM的體積比DRAM大至少4倍。這樣就意味著你沒有足夠空間安放同樣數量的引腳(因為針腳並沒有因此減少4倍)。當然為了安裝同樣數量的針腳,也可以把芯片的體積加大,但是這樣就提高芯片的生產成本和功耗,所以減少針腳數目也是必要的,對於現在的大容量DRAM芯片,多路尋址技術已經是必不可少的了。當然多路尋址技術也使得讀寫的過程更加復雜了,這樣在設計的時候不僅僅DRAM芯片更加復雜了,DRAM接口也要更加復雜,在我們介紹DRAM讀寫過程之前,請大家看一張DRAM芯片內部結構示意圖:在上面的示意圖中,你可以看到在DRAM結構中相對於SRAM多了兩個部分:由/RAS (Row Address Strobe:行地址脈沖選通器)引腳控制的行地址門闩線路(Row Address Latch)和由/CAS(Column Address Strobe:列地址脈沖選通器)引腳控制的列地址門闩線路(Column Address Latch)。 1)通過地址總線將行地址傳輸到地址引腳

2)/RAS引腳被激活,這樣行地址被傳送到行地址門闩線路中

3)行地址解碼器根據接收到的數據選擇相應的行 4)/WE引腳被確定不被激活,所以DRAM知道它不會進行寫入操作

5)列地址通過地址總線傳輸到地址引腳

6)/CAS引腳被激活,這樣列地址被傳送到行地址門闩線路中

7)/CAS引腳同樣還具有/OE引腳的功能,所以這個時候Dout引腳知道需要向外輸出數據。 8) /RAS和/CAS都不被激活,這樣就可以進行下一個周期的數據操作了。其實DRAM的寫入的過程和讀取過程是基本一樣的,所以如果你真的理解了上面的過程就能知道寫入過程了,所以這裡我就不贅述了。(只要把第4步改為/WE引腳被激活就可以了)。我們已經提到過,DRAM同SRAM最大的不同就是不能比較長久的保持數據,這項特性使得這種存儲介質對於我們幾乎沒有任何的作用。但是DRAM設計師利用刷新的技術使得DRAM稱為了現在對於我們最有用處的存儲介質。這裡我僅僅簡要的提及一下DRAM的刷新技術,因為在後面介紹FP、EDO等類型的內存的時候,你會發現它們具體的實現過程都是不同的。 DRAM內僅僅能保持其內存儲的電荷非常短暫的時間,所以它需要在其內的電荷消失之前就進行刷新直到下次寫入數據或者計算機斷電才停止。每次讀寫操作都能刷新DRAM內的電荷,所以DRAM就被設計為有規律的讀取DRAM內的內容。這樣做有下面幾個好處。第一,僅僅使用/RAS激活每一行就可以達到全部刷新的目的;第二,DRAM控制器來控制刷新,這樣可以防止刷新操作干擾有規律的讀寫操作。在文章的開始,我曾經說過一般行的數目比列的數據少。現在我可以告訴為什麼會這樣了,因為行越少用戶刷新的時間就會越少。 OK!時間不早了,今天就先介紹到這裡,希望這裡介紹的DRAM和SRAM的芯片的基本工作原理對你有些幫助。